Kód: 01417773

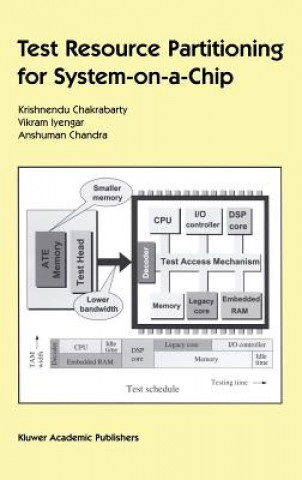

Test Resource Partitioning for System-on-a-Chip

Autor Vikram Iyengar, Anshuman Chandra

Test Resource Partitioning for System-on-a-Chip is about test resource partitioning and optimization techniques for plug-and-play system-on-a-chip (SOC) test automation. Plug-and-play refers to the paradigm in which core-to-core i ... celý popis

- Jazyk:

Angličtina

Angličtina - Vazba: Pevná

- Počet stran: 232

Nakladatelství: Springer-Verlag New York Inc., 2002

- Více informací o knize

3313 Kč

Skladem u dodavatele v malém množství

Odesíláme za 12-15 dnů

Potřebujete více kusů?Máte-li zájem o více kusů, prověřte, prosím, nejprve dostupnost titulu na naši zákaznické podpoře.

Přidat mezi přání

Mohlo by se vám také líbit

-

Inter-Municipal Cooperation in Europe

3313 Kč -

Neurology Self-Assessment: A Companion to Bradley's Neurology in Clinical Practice

1769 Kč -

Katy Perry

307 Kč -

Profesor Con Recursos

713 Kč -

Professor and the Madman

482 Kč -

Maid-sama. Bd.8

150 Kč -

Moral und Sanktion

1204 Kč

Darujte tuto knihu ještě dnes

- Objednejte knihu a zvolte Zaslat jako dárek.

- Obratem obdržíte darovací poukaz na knihu, který můžete ihned předat obdarovanému.

- Knihu zašleme na adresu obdarovaného, o nic se nestaráte.

Více informací o knize Test Resource Partitioning for System-on-a-Chip

Nákupem získáte 331 bodů

Anotace knihy

Anotace knihy

Test Resource Partitioning for System-on-a-Chip is about test resource partitioning and optimization techniques for plug-and-play system-on-a-chip (SOC) test automation. Plug-and-play refers to the paradigm in which core-to-core interfaces as well as core-to-SOC logic interfaces are standardized, such that cores can be easily plugged into "virtual sockets" on the SOC design, and core tests can be plugged into the SOC during test without substantial effort on the part of the system integrator. The goal of the book is to position test resource partitioning in the context of SOC test automation, as well as to generate interest and motivate research on this important topic.§SOC integrated circuits composed of embedded cores are now commonplace. Nevertheless, There remain several roadblocks to rapid and efficient system integration. Test development is seen as a major bottleneck in SOC design, and test challenges are a major contributor to the widening gap between design capability and manufacturing capacity. Testing SOCs is especially challenging in the absence of standardized test structures, test automation tools, and test protocols.§Test Resource Partitioning for System-on-a-Chip responds to a pressing need for a structured methodology for SOC test automation. It presents new techniques for the partitioning and optimization of the three major SOC test resources: test hardware, testing time and test data volume.§Test Resource Partitioning for System-on-a-Chip paves the way for a powerful integrated framework to automate the test flow for a large number of cores in an SOC in a plug-and-play fashion. The framework presented allows the system integrator to reduce test cost and meet short time-to-market requirements.

Parametry knihy

Parametry knihy

Zařazení knihy Knihy v angličtině Technology, engineering, agriculture Electronics & communications engineering Electronics engineering

3313 Kč

- Plný název: Test Resource Partitioning for System-on-a-Chip

- Autor: Vikram Iyengar, Anshuman Chandra

- Jazyk:

Angličtina

Angličtina - Vazba: Pevná

- Počet stran: 232

- EAN: 9781402071195

- ISBN: 1402071191

- ID: 01417773

- Nakladatelství: Springer-Verlag New York Inc.

- Hmotnost: 1170 g

- Rozměry: 235 × 155 × 21 mm

- Datum vydání: 30. June 2002

Oblíbené z jiného soudku

-

The Art of Electronics

2656 Kč -

Practical Electronics for Inventors

969 Kč -

The Art of Electronics: The x Chapters

1725 Kč -

How to Diagnose and Fix Everything Electronic, Second Edition

603 Kč -

Electronic Devices, Circuits, and Applications

1611 Kč -

Practical Electronics - A Self-Teaching Guide

591 Kč -

Practical Electronics: A Complete Introduction

463 Kč -

Lego Power Functions Idea Book, Volume 1

586 Kč -

Design of Analog CMOS Integrated Circuits

2065 Kč -

Automotive Oscilloscopes

1353 Kč -

Signals & Systems For Dummies

518 Kč -

LOGO! 8 - A Practical Introduction, with Circuit Solutions and Example Programs

851 Kč -

LEGO MINDSTORMS EV3 Idea Book

566 Kč -

Encyclopedia of Electronic Components Volume 2

617 Kč -

Probabilistic Robotics

2919 Kč -

Motors for Makers

779 Kč -

Schaum's Outline of Electronic Devices and Circuits, Second Edition

612 Kč -

High-Frequency Magnetic Components 2e

4654 Kč -

Theory of Robot Control

4204 Kč -

Art of Hardware Architecture

3415 Kč -

Introduction to Optimal Control Theory

2422 Kč -

FPGA Design

3234 Kč -

Computer Arithmetic

2998 Kč -

Schaum's Outline of Digital Principles

866 Kč -

Designing with Xilinx (R) FPGAs

3674 Kč -

The LEGO Power Functions Idea Book, Vol. 2

558 Kč -

Complete Electronics Self-Teaching Guide with Projects

731 Kč -

Audiophile Vacuum Tube Amplifiers - Design, Construction, Testing, Repairing & Upgrading, Volume 1

1751 Kč -

Audiophile Vacuum Tube Amplifiers - Design, Construction, Testing, Repairing & Upgrading, Volume 2

1751 Kč -

Audiophile Vacuum Tube Amplifiers Volume 3

1750 Kč -

Lego Technic Idea Book: Simple Machines

480 Kč -

Arduino Cookbook

1126 Kč -

How to Diagnose and Repair Automotive Electrical Systems

617 Kč -

Electronics For Dummies, UK Edition

496 Kč -

High Speed Digital Design

3907 Kč -

Automobile Electrical and Electronic Systems

1577 Kč -

Scary Smart

608 Kč -

3,000 Solved Problems in Electrical Circuits

1014 Kč -

Robotics, Vision and Control

1771 Kč -

Lego Technic Idea Book: Fantastic Contraptions

447 Kč -

Lego Technic Idea Book: Wheeled Wonders

517 Kč -

Cybernetics

376 Kč -

Encyclopedia of Electronic Components

518 Kč -

PLC Controls with Structured Text (ST)

767 Kč -

Make: More Electronics

689 Kč -

Fundamentals of Power Electronics

2571 Kč -

Arduino Projects For Dummies

520 Kč -

C Programming on Raspberry Pi

871 Kč -

Manga Guide To Microprocessors

735 Kč

Osobní odběr Praha, Brno a 12903 dalších

Copyright ©2008-24 nejlevnejsi-knihy.cz Všechna práva vyhrazenaSoukromíCookies

Vrácení do měsíce

Vrácení do měsíce 571 999 099 (8-15.30h)

571 999 099 (8-15.30h)